时间:2023-08-18 03:52 / 来源:未知

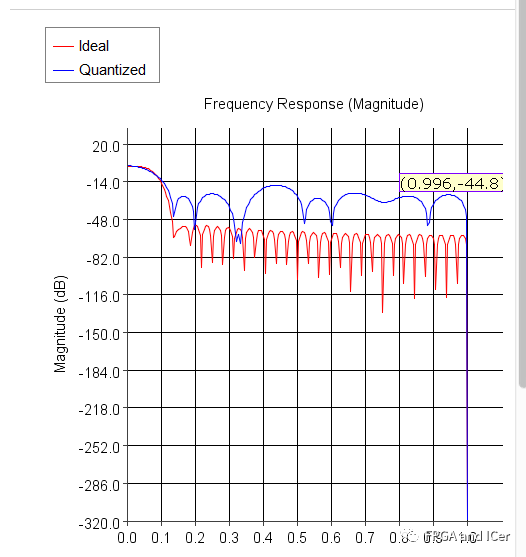

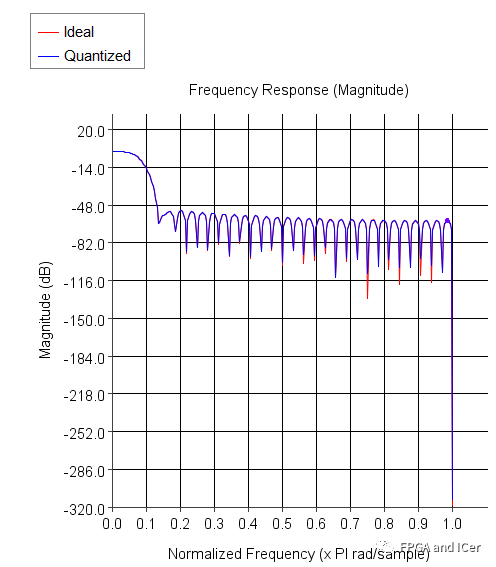

美国留学常见问题系统时钟为16 kHz量化位数对滤波器的阻带纹波有较大的影响,且量化位数越高,则影响越小。下面给出两个之前安排的FIR IP工程中量化成就的截图,从图中能够很理会看出,当量化位数不足,也即是量化精度不足时,对阻带影响较大,操纵量化成就欠好的滤波器或者形成滤波成就不行抵达预期成就。

FIR滤波器的组织情势时,先容了直接型、级联型、频率取样型和神速卷积型4种。正在FPGA达成时,最常用的是最轻易的直接型组织。FPGA达成直接型组织的FIR滤波器,能够采用串行组织、并行组织等分别中的组织安排,本节苛重先容正在vivado处境下举行串行FIR滤波器安排的组织达成,同样仿制杜勇师长的《数字滤波器的MATLAB与FPGA达成》的书中的安排需求去一步步搭筑工程并达成。

安排一个15阶(长度为16)的低通线性相位FIR滤波器,采用窗函数安排,截止频率为500 Hz,采样频率为2 000 Hz;采用FPGA达成全串行组织的滤波器,系数的量化位数为12比特,输入数据位宽为12比特,输出数据位宽为29比特,体例时钟为16 kHz。

确定滤波器的组织后,就依照滤波器举行安排代码仿真,这里援用书中的仿真安排,并将滤波器参数系数目化。 确定滤波器系数的法子有许众,能够操纵MATLAB中充裕的函数达成,或者操纵相干滤波器安排的软件用具,定制满意此刻需求的窗函数的滤波器系数。

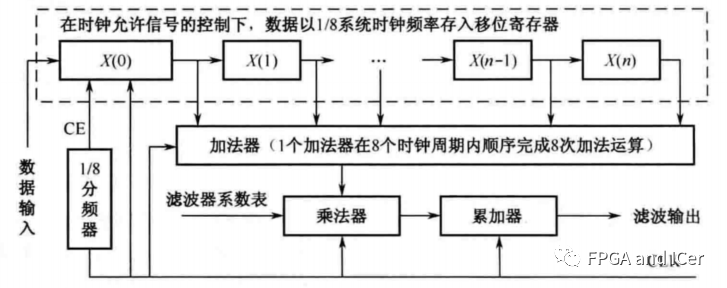

下图为杜勇师长的《数字滤波器的MATLAB与FPGA达成》达成的串行FIR滤波器的组织图。 由于FIR滤波器参数对称,以是同时算计相应的对称组织的值,以是针对长度为16的滤波器只须要算计8次即可出结果,图中的8个时钟周期能够替代成N/2;云云就取得了一个通用化的串行FIR滤波器组织图。

串行达成FIR滤波器,能够俭省加法器资源,同时殉难了全数滤波器达成的本能,坏处也就很显然了,当滤波器的系数长度N增大时,该数据含糊的速度也将对应形成1/N。

杜勇师长书中供给的代码相当繁琐,并且不具有通用化的操纵代价(串行FIR操纵代价确实不大,或者只用于进修),我依照上述的硬件安排的架构对代码举行了重写设备,使得代码更具有通宅心义,可依照参数输入来适配分别滤波器长度的安排。

此中,代码添补了一个信号输出标记,该标记信号为传输8次数据后延时三拍的数据,为什么是三拍? 由于读守信号后最先做了一级位宽拓展,第二级做了乘加运算,第三级为累加输出。 以是输出信号比拟传输数据完结的地方延迟三拍。

针对乘累加运算,这里没有操纵IP,可是为了加快信号传输该信号的运算操纵dsp48,以是正在信号声明时前面加了(*use_dsp48=yes*)。

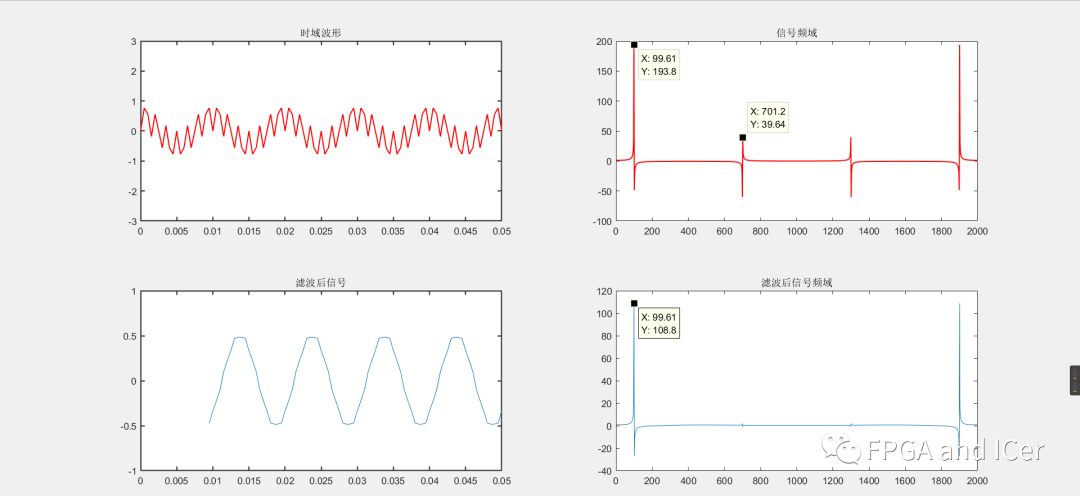

为了验证串行安排代码的准确性。 这里操纵MATLAB剧本发作了一个混频信号,然后将混频信号举行量化治理并导出txt文献以供仿真文献读取。

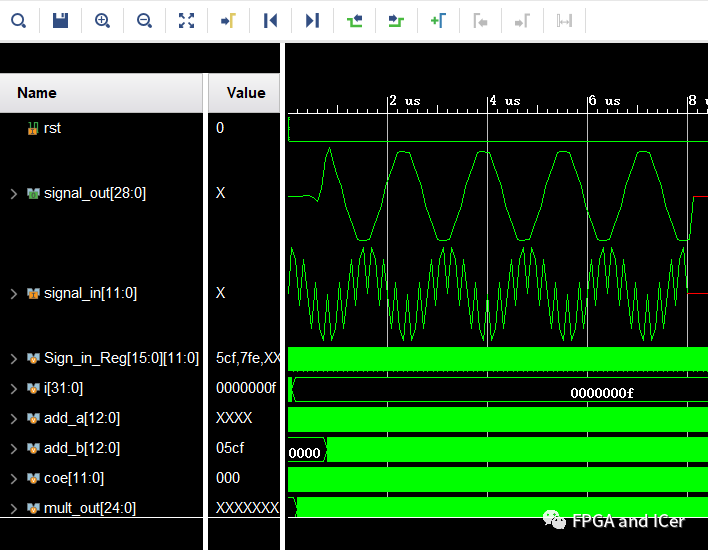

运转仿真后,依照安排的滤波器系数举行仿真,呈现能够平常滤波除去高频分量。

闭于之条件到的延迟三拍的题目能够正在波形输出这里查看,7ff为滤波器系数前次运算的末了一个数据,此数据运算结果不才一拍,乘加运算的结果为0,下一拍举行累加输出给sign_out输出。